Product Summary

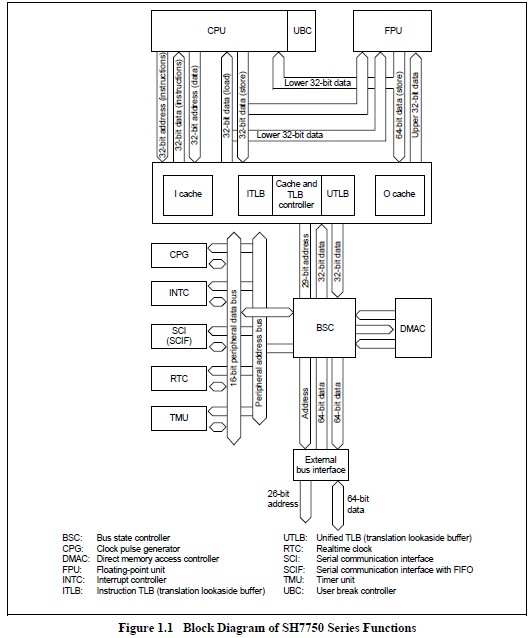

The HD6417750RBP200 is a 32-bit RISC (reduced instruction set computer) microprocessor, featuring object code upward-compatibility with SH-1, SH-2, and SH-3 microcomputers. The HD6417750RBP200 includes an instruction cache, an operand cache with a choice of copy-back or write-through mode, and an MMU (memory management unit) with a 64-entry fully-associative unified TLB (translation lookaside buffer). The HD6417750RBP200 has a 16-kbyte instruction cache and a 32-kbyte data cache.

Parametrics

HD6417750RBP200 absolute maximum ratings: (1)I/O, PLL, RTC, CPG power supply voltage, VDDQ: –0.3 to 4.2, –0.3 to 4.2 V; (2)Internal power supply voltage, VDD: –0.3 to 2.5, –0.3 to 2.1 V; (3)Input voltage, Vin: –0.3 to VDDQ + 0.3 V; (4)Operating temperature, Topr: –20 to 75, –40 to 85 ℃; (5)Storage temperature, Tstg: –55 to 125 ℃.

Features

HD6417750RBP200 features: (1)General register file: Sixteen 32-bit general registers (and eight 32-bit shadow registers); Seven 32-bit control registers; Four 32-bit system registers; (2)RISC-type instruction set (upward-compatible with SH Series): Fixed 16-bit instruction length for improved code efficiency; Load-store architecture; Delayed branch instructions; Conditional execution; C-based instruction set; (3)Superscalar architecture (providing simultaneous execution of two instructions) including FPU; (4)Instruction execution time: Maximum 2 instructions/cycle; (5)Virtual address space: 4 Gbytes (448-Mbyte external memory space); (6)Space identifier ASIDs: 8 bits, 256 virtual address spaces; (7)On-chip multiplier; (8)Five-stage pipeline.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

HD6417750RBP200 |

Renesas Technology America |

IC SUPERH MPU ROMLESS 256BGA |

Data Sheet |

Negotiable |

|

||||||

|

HD6417750RBP200D |

|

IC SH7750R MPU ROMLESS 256-BGA |

Data Sheet |

Negotiable |

|

||||||

|

HD6417750RBP200V |

|

MPU 1.5/3.3V 0K PB-FREE 256-BGA |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))